–Т–≤–µ–і–µ–љ–Є–µ –≤ –Р–¶–Я

(вЖТвАО–Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–є –Р–¶–Я(Flash or parallel ADC)) |

|||

| –°—В—А–Њ–Ї–∞ 6: | –°—В—А–Њ–Ї–∞ 6: | ||

==–Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–є –Р–¶–Я(Flash or parallel ADC)== | ==–Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–є –Р–¶–Я(Flash or parallel ADC)== | ||

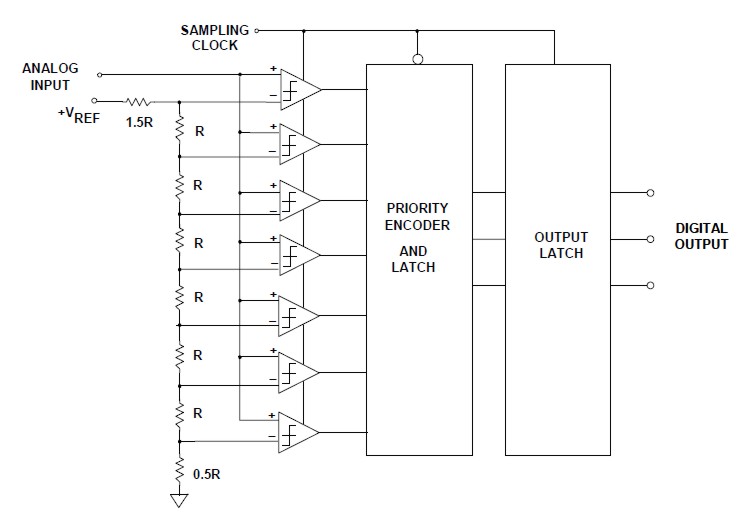

| вИТ | –Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–µ –Р–¶–Я –Є–Љ–µ—О—В —А–∞–Ј—А—П–і–љ–Њ—Б—В—М 6-8 –±–Є—В –њ—А–Є —Б–Ї–Њ—А–Њ—Б—В–Є –і–Њ 1 GSPS(giga | + | –Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–µ –Р–¶–Я –Є–Љ–µ—О—В —А–∞–Ј—А—П–і–љ–Њ—Б—В—М 6-8 –±–Є—В –њ—А–Є —Б–Ї–Њ—А–Њ—Б—В–Є –і–Њ 1 GSPS(giga samples per seconds).–Р—А—Е–Є—В–µ–Ї—В—Г—А–∞ –і–∞–љ–љ–Њ–≥–Њ –≤–Є–і–∞ –Р–¶–Я –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ–љ–∞—П –љ–∞ —А–Є—Б—Г–љ–Ї–µ. |

[[–Ш–Ј–Њ–±—А–∞–ґ–µ–љ–Є–µ:flash_ADC.jpg]] | [[–Ш–Ј–Њ–±—А–∞–ґ–µ–љ–Є–µ:flash_ADC.jpg]] | ||

–Т–µ—А—Б–Є—П 17:17, 19 —Д–µ–≤—А–∞–ї—П 2013

–Р–¶–Я - –∞–љ–∞–ї–Њ–≥–Њ-—Ж–Є—Д—А–Њ–≤–Њ–є –њ—А–µ–Њ–±—А–∞–Ј–Њ–≤–∞—В–µ–ї—М(Analog to Digital, ADC),—Г—Б—В—А–Њ–є—Б—В–≤–Њ, –Ї–Њ—В–Њ—А–Њ–µ –њ—А–µ–Њ–±—А–∞–Ј—Г–µ—В –≤—Е–Њ–і–љ–Њ–є –∞–љ–∞–ї–Њ–≥–Њ–≤—Л–є —Б–Є–≥–љ–∞–ї –≤ –≤—Л—Е–Њ–і–љ–Њ–є —Ж–Є—Д—А–Њ–≤–Њ–є —Б–Є–≥–љ–∞–ї –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ–љ—Л–є,–њ—А–µ–Є–Љ—Г—Й–µ—Б—В–≤–µ–љ–љ–Њ, –≤ –і–≤–Њ–Є—З–љ–Њ–Љ –Ї–Њ–і–µ. –Т—Е–Њ–і–љ—Л–Љ —Б–Є–≥–љ–∞–ї–Њ–Љ –Љ–Њ–ґ–µ—В –±—Л—В—М –њ—А–∞–Ї—В–Є—З–µ—Б–Ї–Є –ї—О–±–∞—П —Д–Є–Ј–Є—З–µ—Б–Ї–∞—П –≤–µ–ї–Є—З–Є–љ–∞, –љ–Њ –і–ї—П –Њ–њ—А–µ–і–µ–ї—С–љ–љ–Њ—Б—В–Є —Г—Б–ї–Њ–≤–Є–Љ—Б—П, —З—В–Њ –≤—Е–Њ–і–љ—Л–Љ —Б–Є–≥–љ–∞–ї–Њ–Љ —П–≤–ї—П–µ—В—Б—П –љ–∞–њ—А—П–ґ–µ–љ–Є–µ.–Ю—Б–љ–Њ–≤–љ—Л–Љ–Є –њ–∞—А–∞–Љ–µ—В—А–∞–Љ–Є –Р–¶–Я —П–≤–ї—П–µ—В—Б—П —А–∞–Ј—А—П–і–љ–Њ—Б—В—М –≤—Л—Е–Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –Є —Б–Ї–Њ—А–Њ—Б—В—М –њ—А–µ–Њ–±—А–∞–Ј–Њ–≤–∞–љ–Є—П.

–Т –і–∞–љ–љ–Њ–є —Б—В–∞—В—М–µ –±—Г–і—Г—В –Ї—А–∞—В–Ї–Њ —А–∞—Б—Б–Љ–Њ—В—А–µ–љ—Л –Њ—Б–љ–Њ–≤–љ—Л–µ –≤–Є–і—Л –Р–¶–Я, –њ—А–µ–і—Б—В–∞–≤–ї—П—О—Й–Є–µ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—О –≤ –і–≤–Њ–Є—З–љ–Њ–Љ –Ї–Њ–і–µ.–Ш –±–Њ–ї–µ–µ –њ–Њ–і—А–Њ–±–љ–Њ –Р–¶–Я, –Ї–Њ—В–Њ—А—Л–µ –њ—А–µ–і—Б—В–∞–≤–ї—П—О—В –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—О –≤ —Б–Є—Б—В–µ–Љ–µ –Њ—Б—В–∞—В–Њ—З–љ—Л—Е –Ї–ї–∞—Б—Б–Њ–≤.

–°–Њ–і–µ—А–ґ–∞–љ–Є–µ |

–Т–Є–і—Л –Р–¶–Я

–Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–є –Р–¶–Я(Flash or parallel ADC)

–Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–µ –Р–¶–Я –Є–Љ–µ—О—В —А–∞–Ј—А—П–і–љ–Њ—Б—В—М 6-8 –±–Є—В –њ—А–Є —Б–Ї–Њ—А–Њ—Б—В–Є –і–Њ 1 GSPS(giga samples per seconds).–Р—А—Е–Є—В–µ–Ї—В—Г—А–∞ –і–∞–љ–љ–Њ–≥–Њ –≤–Є–і–∞ –Р–¶–Я –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ–љ–∞—П –љ–∞ —А–Є—Б—Г–љ–Ї–µ.

–Я—А–Є–љ—Ж–Є–њ–µ —А–∞–±–Њ—В—Л –Њ—В–љ–Њ—Б–Є—В–µ–ї—М–љ–Њ –њ—А–Њ—Б—В. –Э–∞ –Ї–∞–ґ–і—Л–є –Ї–Њ–Љ–њ–∞—А–∞—В–Њ—А –њ–Њ–і–∞—С—В—Б—П –≤—Е–Њ–і–љ–Њ–є –∞–љ–∞–ї–Њ–≥–Њ–≤—Л–є —Б–Є–≥–љ–∞–ї –Є –і–Њ–ї—П –Њ–њ–Њ—А–љ–Њ–≥–Њ –љ–∞–њ—А—П–ґ–µ–љ–Є—П. –°—А–∞–≤–љ–Є–≤–∞—П –Є—Е –і—А—Г–≥ —Б –і—А—Г–≥–Њ–Љ –Ї–∞–ґ–і—Л–є –Њ—В–і–µ–ї—М–љ–Њ –≤–Ј—П—В—Л–є –Ї–Њ–Љ–њ–∞—А–∞—В–Њ—А –≤—Л—А–∞–±–∞—В—Л–≤–∞–µ—В –ї–Њ–≥–Є—З–µ—Б–Ї—Г—О 1 –Є–ї–Є 0 –љ–∞ —Б–≤–Њ—С–Љ –≤—Л—Е–Њ–і–µ, –Ї–Њ—В–Њ—А—Л–µ –њ–Њ—Б—В—Г–њ–∞—О—В –≤ –њ—А–Є–Њ—А–Є—В–µ—В–љ—Л–є —И–Є—Д—А–∞—В–Њ—А(priority encoder).

- –Ф–Њ—Б—В–Њ–Є–љ—Б—В–≤–∞:

- –Я—А–Њ—Б—В–∞—П –∞—А—Е–Є—В–µ–Ї—В—Г—А–∞ –Є –њ—А–Є–љ—Ж–Є–њ —А–∞–±–Њ—В—Л.

- –Т—Л—Б–Њ–Ї–∞—П —Б–Ї–Њ—А–Њ—Б—В—М —А–∞–±–Њ—В—Л.

- –Э–µ–і–Њ—Б—В–∞—В–Ї–Є:

- –Ь–∞–ї–µ–љ—М–Ї–∞—П —А–∞–Ј—А—П–і–љ–Њ—Б—В—М.–Я—А–Є –њ–Њ–≤—Л—И–µ–љ–Є–Є —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Љ–Њ—Й–љ–Њ—Б—В—М –Є –њ–ї–Њ—Й–∞–і—М –љ–∞ –Ї—А–Є—Б—В–∞–ї–ї–µ —А–∞—Б—В—Г—В —Б–ї–Є—И–Ї–Њ–Љ –±—Л—Б—В—А–Њ.

–Ш–љ—В–µ—А–њ–Њ–ї—П—Ж–Є–Њ–љ–љ—Л–є –Р–¶–Я(Interpolating Flash ADC)

–ѓ–≤–ї—П–µ—В—Б—П –ї–Њ–≥–Є—З–µ—Б–Ї–Є–Љ —А–∞–Ј–≤–Є—В–Є–µ–Љ –њ–∞—А–∞–ї–ї–µ–ї—М–љ–Њ–≥–Њ –Р–¶–Я –Є –њ—А–Є–Ј–≤–∞–љ —Г–њ—А–Њ—Б—В–Є—В—М –∞–њ–њ–∞—А–∞—В–љ–Њ–µ —Г—Б–ї–Њ–ґ–љ–µ–љ–Є–µ –њ—А–Є –њ–Њ–≤—Л—И–µ–љ–Є–Є —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є,–∞ –Ј–љ–∞—З–Є—В –њ–Њ–≤—Л—Б–Є—В—М –Њ–±—Й—Г—О —Н—Д—Д–µ–Ї—В–Є–≤–љ–Њ—Б—В—М –њ—А–µ–Њ–±—А–∞–Ј–Њ–≤–∞–љ–Є—П. –Ю—Б–љ–Њ–≤–љ–∞—П –Є–і–µ—П —Б–Њ—Б—В–Њ–Є—В –≤ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–Є –њ—А–µ–і—Г—Б–Є–ї–Є—В–µ–ї–µ–є –≤ –Ї–∞—З–µ—Б—В–≤–µ –ї–Є–љ–µ–є–љ—Л—Е —Г—Б–Є–ї–Є—В–µ–ї–µ–є. –Э–∞ —А–Є—Б—Г–љ–Ї–µ –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ 3-–±–Є—В–љ—Л–є –Є–љ—В–µ—А–њ–Њ–ї—П—Ж–Є–Њ–љ–љ—Л–є –Р–¶–Я.

–Ф–≤—Г—Е—Б—В—Г–њ–µ–љ—З–∞—В—Л–є –Р–¶–Я

–Х—Й—С –Њ–і–љ–Њ —А–∞–Ј–≤–Є—В–Є–µ –њ–∞—А–∞–ї–ї–µ–ї—М–љ–Њ–≥–Њ –Р–¶–Я.–Э–∞–Є–±–Њ–ї–µ–µ –њ–Њ–њ—Г–ї—П—А–љ–∞—П –∞—А—Е–Є—В–µ–Ї—В—Г—А–∞, –Њ–±–µ—Б–њ–µ—З–Є–≤–∞—О—Й–∞—П –≤—Л—Б–Њ–Ї—Г—О —Б–Ї–Њ—А–Њ—Б—В—М –њ—А–µ–Њ–±—А–∞–Ј–Њ–≤–∞–љ–Є—П –Є —Б—А–µ–і–љ–µ–µ —А–∞–Ј—А–µ—И–µ–љ–Є–µ. –Э–∞ –њ–µ—А–≤–Њ–Љ —И–∞–≥–µ –∞–љ–∞–ї–Њ–≥–Њ–≤—Л–є —Б–Є–≥–љ–∞–ї –њ–Њ–і–∞—С—В—Б—П –љ–∞ n-—А–∞–Ј—А—П–і–љ—Л–є –Р–¶–Я,–Ї–Њ—В–Њ—А—Л–є –і–µ–ї–∞–µ—В –≥—А—Г–±–Њ–µ –њ—А–µ–Њ–±—А–∞–Ј–Њ–≤–∞–љ–Є–µ –Є –≤—Л—А–∞–±–∞—В—Л–≤–∞–µ—В n —Б—В–∞—А—И–Є—Е –±–Є—В–Њ–≤ –Ї–Њ–і–∞(MSB - Most Significant Bit). –≠—В–∞ –ґ–µ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—П –њ–Њ–њ–∞–і–∞–µ—В –≤ –¶–Р–Я –Є –њ—А–µ–Њ–±—А–∞–Ј—Г–µ—В—Б—П –Њ–±—А–∞—В–љ–Њ –≤ –∞–љ–∞–ї–Њ–≥–Њ–≤—Л–є –≤–Є–і, –Ї–Њ—В–Њ—А—Л–є –Ј–∞—В–µ–Љ –≤—Л—З–Є—В–∞–µ—В—Б—П –Є–Ј –њ–µ—А–≤–Њ–љ–∞—З–∞–ї—М–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞. –Ю—Б—В–∞—В–Њ–Ї –њ—А–µ–Њ–±—А–∞–Ј—Г–µ—В—Б—П –Р–¶–Я —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є m –Є –≤—Л—А–∞–±–∞—В—Л–≤–∞–µ—В—Б—П m –Љ–ї–∞–і—И–Є—Е –±–Є—В–Њ–≤(LSB, Lowest Significant Bit).–Т –Є—В–Њ–≥–µ –њ–Њ–ї—Г—З–∞–µ—В—Б—П —Ж–Є—Д—А–Њ–≤–Њ–є —Б–Є–≥–љ–∞–ї —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є P=n+m.

- –Ф–Њ—Б—В–Њ–Є–љ—Б—В–≤–∞:

- –£–Љ–µ–љ—М—И–µ–љ–Є–µ –∞–њ–њ–∞—А–∞—В–љ—Л—Е –Ј–∞—В—А–∞—В(30 –Ї–Њ–Љ–њ–∞—А–∞—В–Њ—А–Њ–≤ –≤ –і–≤—Г—Е—Б—В—Г–њ–µ–љ—З–∞—В–Њ–Љ –Р–¶–Я –њ—А–Њ—В–Є–≤ 255 –≤ –Њ–±—Л—З–љ–Њ–Љ –і–ї—П –њ–Њ–ї—Г—З–µ–љ–Є—П 8-—А–∞–Ј—А—П–і–љ—Л—Е —З–Є—Б–µ–ї).

- –£–Љ–µ–љ—М—И–µ–љ–Є–µ –њ–Њ—В—А–µ–±–ї–µ–љ–Є—П –Є –≤—Е–Њ–і–љ–Њ–є —С–Љ–Ї–Њ—Б—В–Є.

- –Э–µ–і–Њ—Б—В–∞—В–Ї–Є:

- –С–Њ–ї–µ–µ –≤—Л—Б–Њ–Ї–∞—П –Ј–∞–і–µ—А–ґ–Ї–∞ –≤ —Б—А–∞–≤–љ–µ–љ–Є–Є —Б –Њ–±—Л—З–љ—Л–Љ –њ–∞—А–∞–ї–ї–µ–ї—М–љ—Л–Љ –Р–¶–Я.

- –Э–µ–Њ–±—Е–Њ–і–Є–Љ–Њ—Б—В—М –њ—А–Є–Љ–µ–љ–µ–љ–Є—П –¶–Р–Я –±–Њ–ї—М—И–µ–є —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є —З–µ–Љ P.