Комплексное исследование умножителей в диапазоне 3 - 64 бит

DimaT (обсуждение | вклад) |

DimaT (обсуждение | вклад) |

||

| Строка 32: | Строка 32: | ||

[[Изображение:ultra1.JPG]] | [[Изображение:ultra1.JPG]] | ||

| + | [[Изображение:ultra2.JPG]] | ||

| + | [[Изображение:ultra3.JPG]] | ||

[1] [http://opencores.org/websvn,filedetails?repname=pyramid_unit&path=%2Fpyramid_unit%2Ftrunk%2FInteger+multiplication+algorithms.pdf Vladimir V.Erokhin "Integer multiplication algorithms. Methodology and implementation results"] | [1] [http://opencores.org/websvn,filedetails?repname=pyramid_unit&path=%2Fpyramid_unit%2Ftrunk%2FInteger+multiplication+algorithms.pdf Vladimir V.Erokhin "Integer multiplication algorithms. Methodology and implementation results"] | ||

Версия 14:44, 16 мая 2013

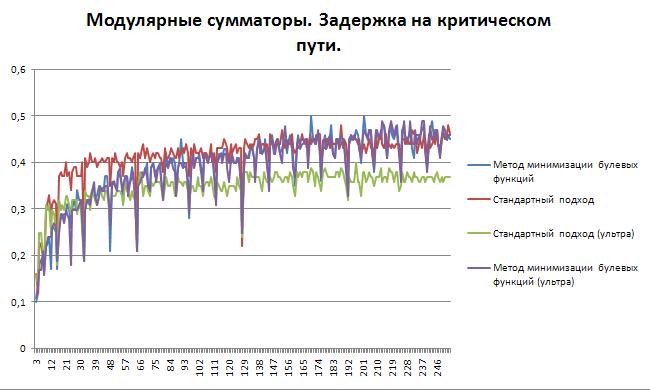

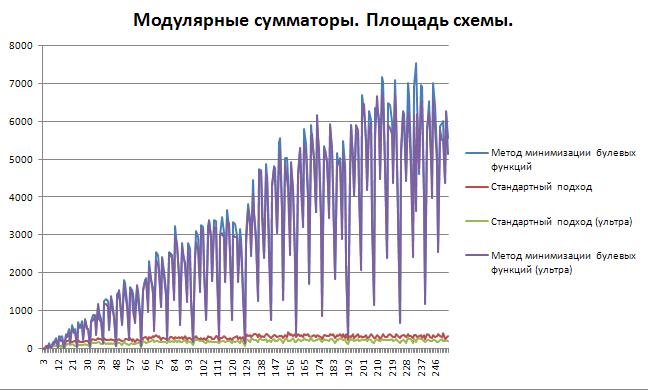

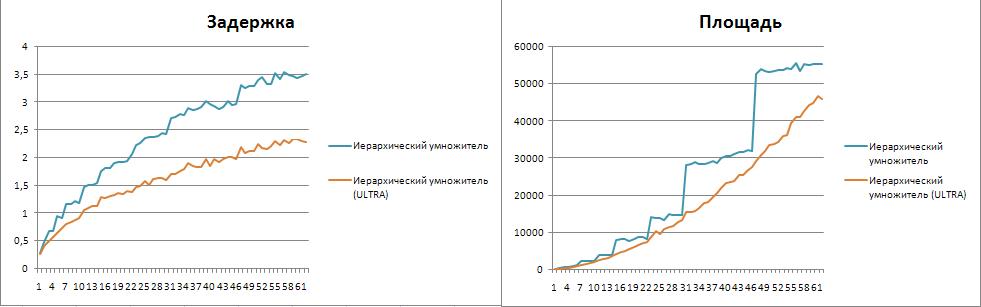

В рамках работы по разработке эффективных модулярных устройств было проведено исследование различных вариантов построения однотактовых двоичных и модулярных умножителей с входными операндами в диапазоне 3-64 бит. Такие устройства чрезвычайно важны в современной микроэлектронике. Каждый современный микропроцессор имеет такую операцию в составе своего набора инструкций, а продвинутые DSP процессоры содержат специальные вычислительные блоки для ускоренного вычисления [1]. Исследовались 4 варианта однотактовых умножителей:

- Встроенный умножитель в САПР Synopsys Design Compiler.

- Иерархический двоичный умножитель [1].

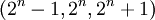

- Модулярный умножитель со стандартным спец. базисом из трех модулей (3 moduli set)

- Модулярный умножитель с продвинутым спец. базисом из 4-х модулей (3 moduli set)

Синтез проводился в базисе 45 нм. в библиотеке NangateOpenCellLibrary.lib с помощью САПР Synopsys Design Compiler. Синтез проводился дважды для каждой из схем, на разных настройках "усилий" синтезатора - medium и ultra high effort. Таким образом, также проверялась способность САПРа по минимизации задержек для различных схем. Таким образом, общее количество тестов выглядит следующим образом.

| Модулярный | Двоичный | ||||||

| 3 moduli set | 4 moduli set | Встроенный | Иерархический | ||||

| medium effort | ultra effort | medium effort | ultra effort | medium effort | ultra effort | medium effort | ultra effort |

Анализ эффективности САПР в режиме ULTRA high effort

[1] Vladimir V.Erokhin "Integer multiplication algorithms. Methodology and implementation results"