Модулярное АЦП

(Новая страница: «В данной статье рассмотрены различные архитектуры модулярного АЦП(A/R), а так же их сравне…») |

(→АЦП последовательного приближения) |

||

| (не показаны 15 промежуточных версий 1 участника) | |||

| Строка 1: | Строка 1: | ||

В данной статье рассмотрены различные архитектуры модулярного АЦП(A/R), а так же их сравнение между собой. | В данной статье рассмотрены различные архитектуры модулярного АЦП(A/R), а так же их сравнение между собой. | ||

| − | =Flash A/R Converter= | + | =Виды АЦП= |

| + | ==Flash A/R Converter== | ||

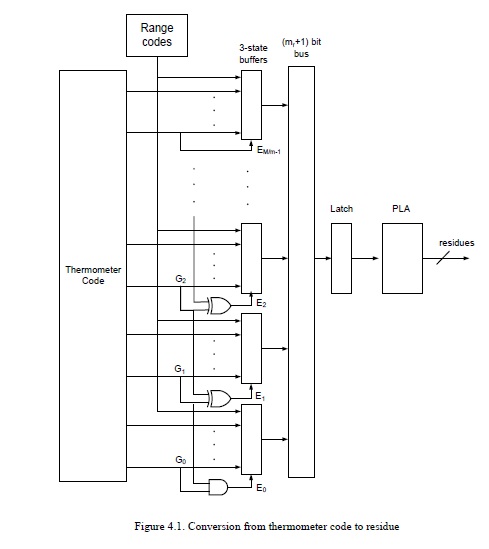

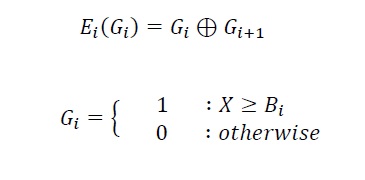

Идеология абсолютно такая же, как и для обыкновенного АЦП.Для построения n-битного модулярного АЦП необходимо 2<sup>n</sup>-1 компараторов и 2<sup>n</sup> резисторов. Разница между модулярным и позиционным АЦП заключается в декодере. Ниже приведена схема для декодера унарного кода в модулярное представление. | Идеология абсолютно такая же, как и для обыкновенного АЦП.Для построения n-битного модулярного АЦП необходимо 2<sup>n</sup>-1 компараторов и 2<sup>n</sup> резисторов. Разница между модулярным и позиционным АЦП заключается в декодере. Ниже приведена схема для декодера унарного кода в модулярное представление. | ||

| + | [[Изображение:Thermometer_code.jpg]][[Изображение:Thermometer_code_2.jpg]] | ||

| − | [[Изображение: | + | Для любого входного значения X из M только один XOR будет на выходе генерировать логическую единицу,тем самым активируя буфер.Выход из каждого буфера является искомым остатком операции деления X по модулю mr.После этого данные попадают в ПЛМ(PLA) размерности mr на log2(mr-1). |

| + | |||

| + | Задержка распространения сигнала в модулярном АЦП определяется 4 параметрами: | ||

| + | *задержкой компаратора | ||

| + | *задержкой XOR | ||

| + | *задержкой буфера | ||

| + | *задержкой ПЛМ | ||

| + | |||

| + | Задержку позиционного АЦП определяет всего 2 параметра: | ||

| + | *задержка компаратора | ||

| + | *задержка ROM | ||

| + | |||

| + | Как правило,для больших чисел сумма задержки буфера,XOR и ПЛМ много меньше задержки ROM. | ||

| + | |||

| + | ===Iterative flash A/R converter=== | ||

| + | |||

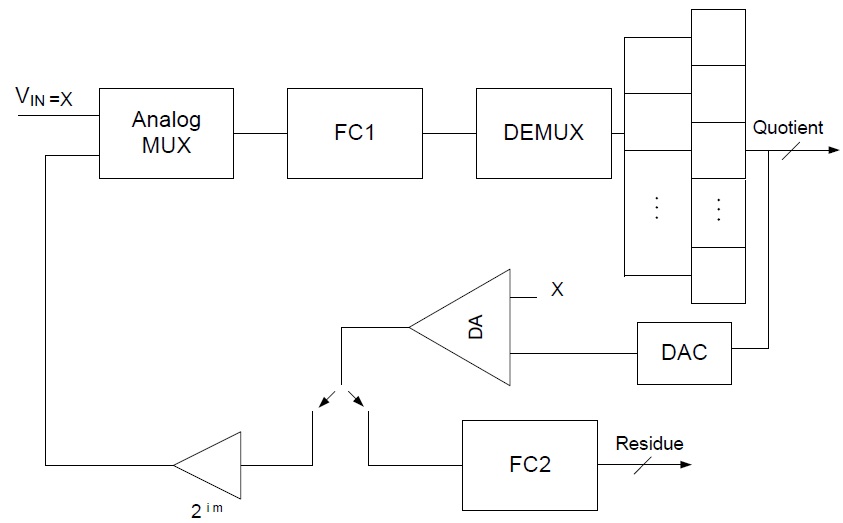

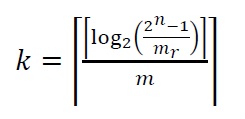

| + | Схема является двухступенчатой: на первом этапе генерируется базовое значение,на втором остатки от деления.Аналоговый сигнал делится и подаётся на первый конвертер(FC1), который генерирует m старших битов частного. Они записываются в первый регистр(R1) при помощи мультиплексора.Далее начинается вторая стадия. Бинарное представление частного конвертируется в аналоговую форму и дифференциальный усилитель,на второй вход которого подаётся изначальный аналоговый сигнал. Далее происходит конвертирование аналогового сигнала в цифровое представление на FC2, которое и является модулярным видом числа. Процесс повторяется k раз,где k: | ||

| + | [[Изображение:K.jpg]] | ||

| + | |||

| + | [[Изображение:Iterative_ARC.jpg]] | ||

| + | |||

| + | ===Двухступенчатый АЦП=== | ||

| + | |||

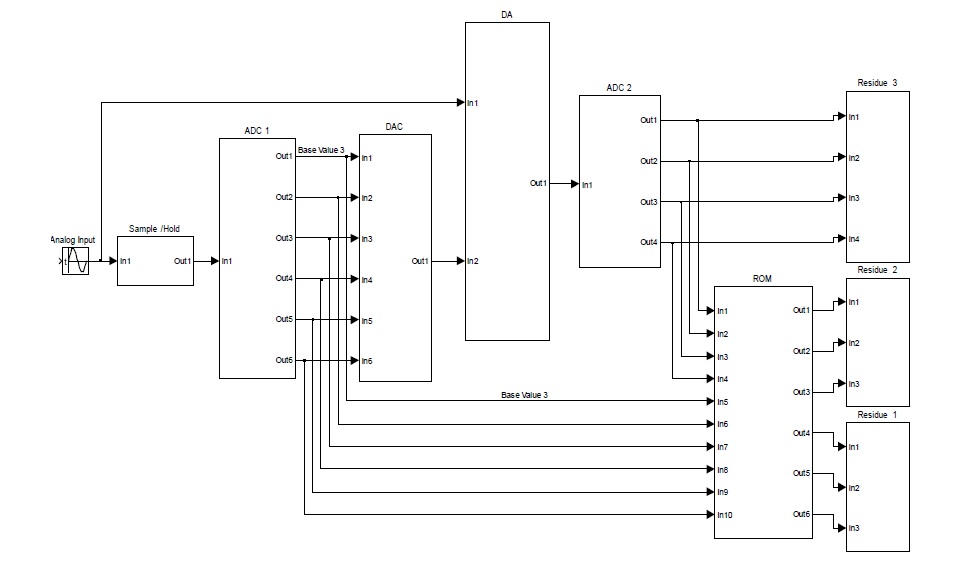

| + | На картинке ниже представлена архитектура АЦП,использующая модули {7,8,9}. Принцип работы очень похож на итерационный АЦП с той лишь разницей,что всё делается за 1 цикл. Остаток по модулю m3 являетcя выходом из конвертера ADC2. Два других остатка вычисляются по таблице. Использование этой таблицы удерживает на том же уровне энергопотребление и площадь,но создаёт дополнительную задержку. | ||

| + | [[Изображение:Simulink_model.jpg]] | ||

| + | |||

| + | ==АЦП последовательного приближения== | ||

| + | Основная идея такая же как и при конвертировании в бинарное представление. Разница заключается в следующем: | ||

| + | *компаратор заменён на дифференциальный усилитель | ||

| + | *для генерации непосредственно остатков используется второй конвертер | ||

| + | *ЦАП изменён таким образом чтобы усиливать выход в mr раз,где mr - выбранный модуль. | ||

| + | |||

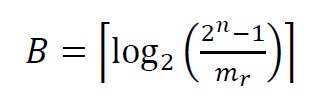

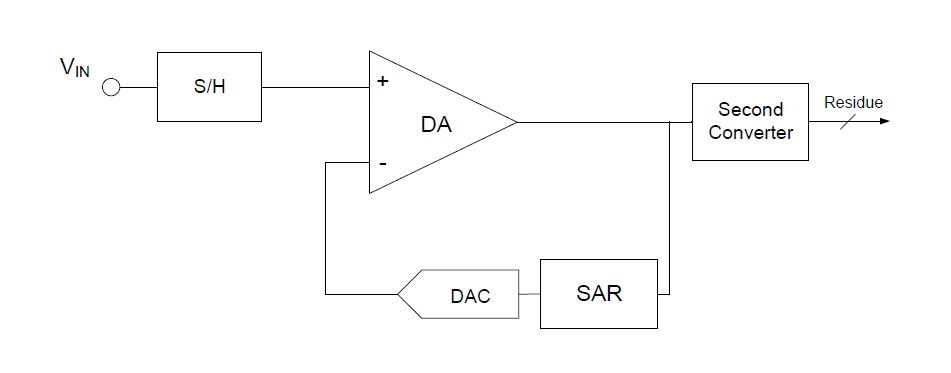

| + | Преобразование длится B+1 цикл, где И это количество битов в SAR, и разрешение n выбирается из условия M>=2<sup>n</sup> [[Изображение:B.jpg]] | ||

| + | [[Изображение:Aproxim_ARC.jpg]] | ||

Текущая версия на 14:47, 11 марта 2013

В данной статье рассмотрены различные архитектуры модулярного АЦП(A/R), а так же их сравнение между собой.

Содержание |

[править] Виды АЦП

[править] Flash A/R Converter

Идеология абсолютно такая же, как и для обыкновенного АЦП.Для построения n-битного модулярного АЦП необходимо 2n-1 компараторов и 2n резисторов. Разница между модулярным и позиционным АЦП заключается в декодере. Ниже приведена схема для декодера унарного кода в модулярное представление.

Для любого входного значения X из M только один XOR будет на выходе генерировать логическую единицу,тем самым активируя буфер.Выход из каждого буфера является искомым остатком операции деления X по модулю mr.После этого данные попадают в ПЛМ(PLA) размерности mr на log2(mr-1).

Задержка распространения сигнала в модулярном АЦП определяется 4 параметрами:

- задержкой компаратора

- задержкой XOR

- задержкой буфера

- задержкой ПЛМ

Задержку позиционного АЦП определяет всего 2 параметра:

- задержка компаратора

- задержка ROM

Как правило,для больших чисел сумма задержки буфера,XOR и ПЛМ много меньше задержки ROM.

[править] Iterative flash A/R converter

Схема является двухступенчатой: на первом этапе генерируется базовое значение,на втором остатки от деления.Аналоговый сигнал делится и подаётся на первый конвертер(FC1), который генерирует m старших битов частного. Они записываются в первый регистр(R1) при помощи мультиплексора.Далее начинается вторая стадия. Бинарное представление частного конвертируется в аналоговую форму и дифференциальный усилитель,на второй вход которого подаётся изначальный аналоговый сигнал. Далее происходит конвертирование аналогового сигнала в цифровое представление на FC2, которое и является модулярным видом числа. Процесс повторяется k раз,где k:

[править] Двухступенчатый АЦП

На картинке ниже представлена архитектура АЦП,использующая модули {7,8,9}. Принцип работы очень похож на итерационный АЦП с той лишь разницей,что всё делается за 1 цикл. Остаток по модулю m3 являетcя выходом из конвертера ADC2. Два других остатка вычисляются по таблице. Использование этой таблицы удерживает на том же уровне энергопотребление и площадь,но создаёт дополнительную задержку.

[править] АЦП последовательного приближения

Основная идея такая же как и при конвертировании в бинарное представление. Разница заключается в следующем:

- компаратор заменён на дифференциальный усилитель

- для генерации непосредственно остатков используется второй конвертер

- ЦАП изменён таким образом чтобы усиливать выход в mr раз,где mr - выбранный модуль.

Преобразование длится B+1 цикл, где И это количество битов в SAR, и разрешение n выбирается из условия M>=2n