Исследование позиционного умножения на нашей библиотеке — различия между версиями

Материал из Модулярная арифметики

Turbo (обсуждение | вклад) |

Turbo (обсуждение | вклад) |

||

| (не показана одна промежуточная версия этого же участника) | |||

| Строка 30: | Строка 30: | ||

report_area > area_dif_multipliers_12_12.rpt | report_area > area_dif_multipliers_12_12.rpt | ||

report_power -analysis_effort high > power_dif_multipliers_12_12.rpt | report_power -analysis_effort high > power_dif_multipliers_12_12.rpt | ||

| − | remove_design | + | remove_design -all |

</pre> | </pre> | ||

| Строка 38: | Строка 38: | ||

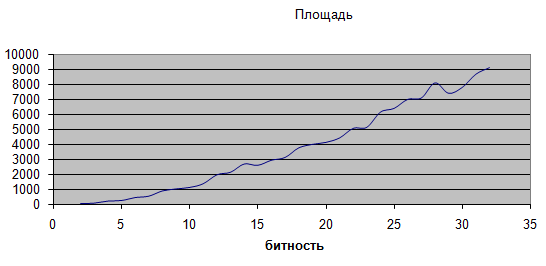

[[Изображение:Std-Mul-Area.png]] | [[Изображение:Std-Mul-Area.png]] | ||

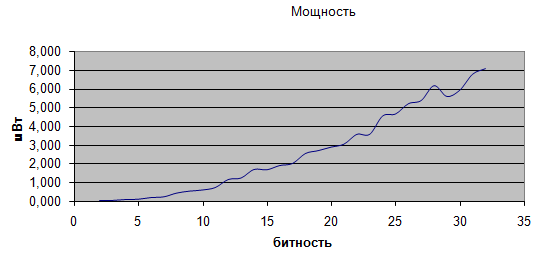

[[Изображение:Std-Mul-Power.png]] | [[Изображение:Std-Mul-Power.png]] | ||

| + | |||

| + | [[Категория:Результаты]] | ||

Текущая версия на 11:42, 20 февраля 2013

Запуск производился на Synopsys Design Compiler.

Verilog-модуль вида

module dif_multipliers_12_12 (a,b,out); output wire [23:0] out; input wire [11:0] a,b; assign out=a*b; endmodule

Библиотека стандартных ячеек

NangateOpenCellLibrary_typical_conditional_nldm.lib

Скрипт для запуска

analyze -f verilog dif_multipliers_12_12.v elaborate dif_multipliers_12_12 uniquify current_design dif_multipliers_12_12 check_design set_load [load_of [get_lib_pins NangateOpenCellLibrary/INV_X4/A]] [all_outputs] set_driving_cell -lib_cell DFFRS_X2 -library NangateOpenCellLibrary -pin Q [all_inputs] set_max_delay -to [all_outputs] 0 set_max_area 0 compile report_timing -significant_digits 6 > timing_dif_multipliers_12_12.rpt report_area > area_dif_multipliers_12_12.rpt report_power -analysis_effort high > power_dif_multipliers_12_12.rpt remove_design -all