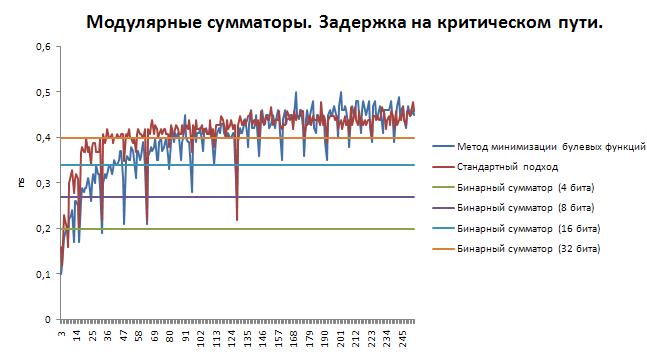

Результат сравнения различных методов построения модулярных умножителей (индексный метод, разность квадратов, метод Espresso)

Было проведено сравнение модулярных умножителей. Рассматриваемые методы:

- Метод минимизации логических функций на базе алгоритма Espresso

- Метод разности квадратов

- Индексная реализация умножителя

Метод Espresso заключается в построении таблицы истинности для операции модулярного умножения, и дальнейшей минимизации получившейся булевой функции методом Espresso. Сравнение проводилось для расширенного набора оснований в диапазоне 3-149. Индексный метод работает только для простых чисел, метод, основанный на разности квадратов допускает любые нечетные числа, а метод Espresso работает для любых целых чисел. Маршрут проектирования для схем Espresso включал минимизацию булевых функций с помощью программного средства Logic Friday. Для автоматизации запуска Logic Friday использовался язык автоматизации AutoIt. Для остальных двух схем использовался стандартный подход с реализацией автоматизироанных генераторов.

Содержание

Типовые Verilog-модули

1. Стандартный модулярный сумматор (на примере модуля 11)

// Sum modulo 11

module sum_modulo_11 (A, B, S);

input [3:0] A;

input [3:0] B;

output reg[3:0] S;

always @(A or B)

begin

if ({1'b0, A} + {1'b0, B} < 11) S <= {1'b0, A} + {1'b0, B};

else S <= {1'b0, A} + {1'b0, B} - (11);

// else S <= {1'b0, A} + {1'b0, B} + (5);

end

endmodule

2. Модулярный сумматор по методу Espresso (на примере модуля 7)

module adder_mod7 (out, a, b); // Сумматор input [2:0] a, b; output [2:0] out; assign out[2] = (~a[2]&~a[1]&~a[0]&b[2]) | (a[2]&a[1]&b[2]&b[1]) | (a[2]&a[0]&b[2]&b[1]) | (~a[2]&a[1]&~b[2]&b[1]) | (~a[2]&~a[1]&b[2]&~b[1]) | (a[2]&~a[1]&~b[2]&~b[1]) | (a[2]&a[1]&b[2]&b[0]) | (a[1]&a[0]&~b[2]&b[0]) | (~a[2]&a[0]&b[1]&b[0]) | (a[2]&~b[2]&~b[1]&~b[0]) | (a[2]&~a[1]&~a[0]&~b[2]&~b[0]) | (~a[2]&~a[0]&b[2]&~b[1]&~b[0]); assign out[1] = (~a[2]&~a[1]&~a[0]&b[1]) | (a[1]&a[0]&b[2]&b[1]) | (a[2]&a[0]&b[2]&~b[1]) | (a[2]&~a[1]&b[2]&b[0]) | (a[2]&a[1]&b[1]&b[0]) | (a[1]&a[0]&b[1]&b[0]) | (~a[1]&a[0]&~b[1]&b[0]) | (~a[1]&~a[0]&b[1]&~b[0]) | (a[1]&~a[0]&~b[1]&~b[0]) | (a[1]&~b[2]&~b[1]&~b[0]) | (~a[2]&a[1]&~a[0]&~b[2]&~b[1]) | (~a[2]&~a[1]&~b[2]&b[1]&~b[0]); assign out[0] = (a[1]&~a[0]&b[2]&b[1]) | (~a[2]&~a[1]&~a[0]&b[0]) | (a[2]&a[0]&b[2]&b[0]) | (a[1]&a[0]&b[2]&b[0]) | (~a[2]&~a[0]&~b[2]&b[0]) | (a[2]&a[0]&b[1]&b[0]) | (a[2]&~a[0]&b[2]&~b[0]) | (~a[2]&a[0]&~b[2]&~b[0]) | (a[2]&a[1]&b[1]&~b[0]) | (a[0]&~b[2]&~b[1]&~b[0]) | (~a[1]&~a[0]&~b[2]&~b[1]&b[0]) | (~a[2]&~a[1]&a[0]&~b[1]&~b[0]); endmodule

Библиотека стандартных ячеек

NangateOpenCellLibrary.lib

Скрипт для запуска

lappend search_path "../libs" "../src" set target_library "NangateOpenCellLibrary.db" set link_library [list "*" $target_library] analyze -f <имя модуля>.v elaborate <имя модуля> uniquify current_design <имя модуля> check_design set_load [load_of [get_lib_pins NangateOpenCellLibrary/INV_X4/A]] [all_outputs] set_driving_cell -lib_cell DFFRS_X2 -library NangateOpenCellLibrary -pin Q [all_inputs] set_max_delay -to [all_outputs] 0 set_max_area 0 compile report_timing > result/timing_<имя модуля>.rpt report_area > result/area_<имя модуля>.rpt remove_design -all

Файлы для эксперимента

- Несжатые таблицы истинности для сумматоров (.csv, 2MB)

- Сжатые Espresso таблицы истинности для сумматоров (.csv, 3MB)

- Verilog на основе таблиц истинности для сумматоров (.csv, 3MB)