Введение в АЦП

АЦП - аналого-цифровой преобразователь(Analog to Digital, ADC), устройство, которое преобразует входной аналоговый сигнал в выходной цифровой сигнал представленный, преимущественно, в двоичном коде. Входным сигналом может быть практически любая физическая величина, но для определённости условимся, что входным сигналом является напряжение. Основными параметрами АЦП является разрядность выходного сигнала и скорость преобразования.

В данной статье будут кратко рассмотрены основные виды АЦП, представляющие информацию в двоичном коде. И более подробно АЦП, которые представляют информацию в системе остаточных классов.

Содержание

Виды АЦП

Параллельный АЦП (Flash or parallel ADC)

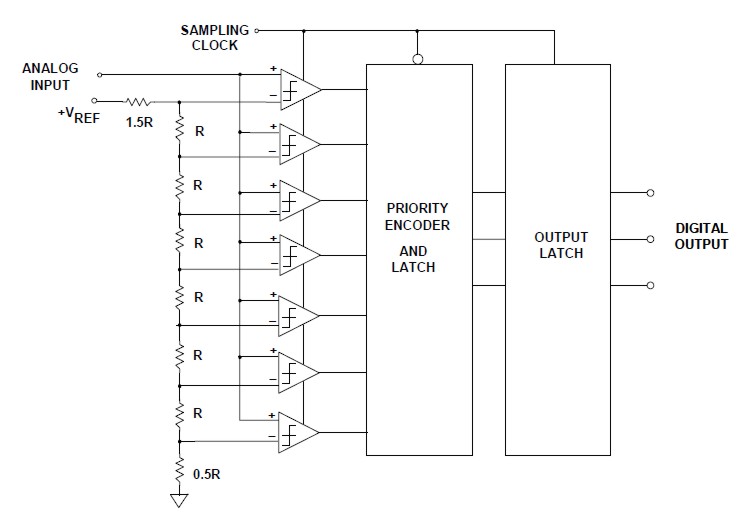

Параллельные АЦП имеют разрядность 6-8 бит при скорости до 1 GSPS (giga samples per seconds). Архитектура данного вида АЦП представленная на рисунке.

Принципе работы относительно прост. На каждый компаратор подаётся входной аналоговый сигнал и доля опорного напряжения. Сравнивая их друг с другом каждый отдельно взятый компаратор вырабатывает логическую 1 или 0 на своём выходе, которые поступают в приоритетный шифратор (priority encoder).

- Достоинства:

- Простая архитектура и принцип работы.

- Высокая скорость работы.

- Недостатки:

- Маленькая разрядность. При повышении разрядности потребляемая мощность и площадь на кристалле растут слишком быстро.

Интерполяционный АЦП (Interpolating Flash ADC)

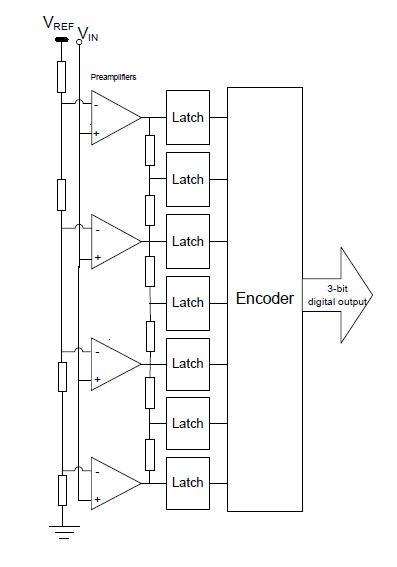

Является логическим развитием параллельного АЦП и призван упростить аппаратное усложнение при повышении разрядности,а значит повысить общую эффективность преобразования. Основная идея состоит в использовании предусилителей в качестве линейных усилителей. На рисунке представлен 3-битный интерполяционный АЦП.

- Достоинства:

- Высокое быстродействие.

- Отсутствие необходимости использовать ЦАП.

- Меньшая входная ёмкость.

- Недостатки:

- Маленькое разрешение.

- Энергопотребление экспоненциально растёт с ростом разрешения.

Двухступенчатый АЦП (Two-stage flash ADC)

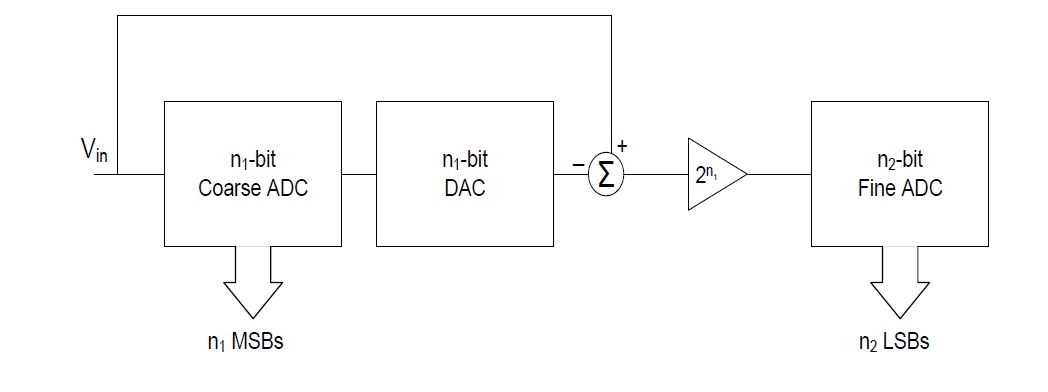

Ещё одно развитие параллельного АЦП. Наиболее популярная архитектура, обеспечивающая высокую скорость преобразования и среднее разрешение. На первом шаге аналоговый сигнал подаётся на n-разрядный АЦП, который делает грубое преобразование и вырабатывает n старших битов кода(MSB - Most Significant Bit). Эта же информация попадает в ЦАП и преобразуется обратно в аналоговый вид, который затем вычитается из первоначального сигнала. Остаток преобразуется АЦП разрядности m и вырабатывается m младших битов (LSB, Lowest Significant Bit). В итоге получается цифровой сигнал разрядности P = n+m.

- Достоинства:

- Уменьшение аппаратных затрат (30 компараторов в двухступенчатом АЦП против 255 в обычном для получения 8-разрядных чисел).

- Уменьшение потребления и входной ёмкости.

- Недостатки:

- Более высокая задержка в сравнении с обычным параллельным АЦП.

- Необходимость применения ЦАП большей разрядности чем P.

Конвейерный АЦП (Pepilined ADC)

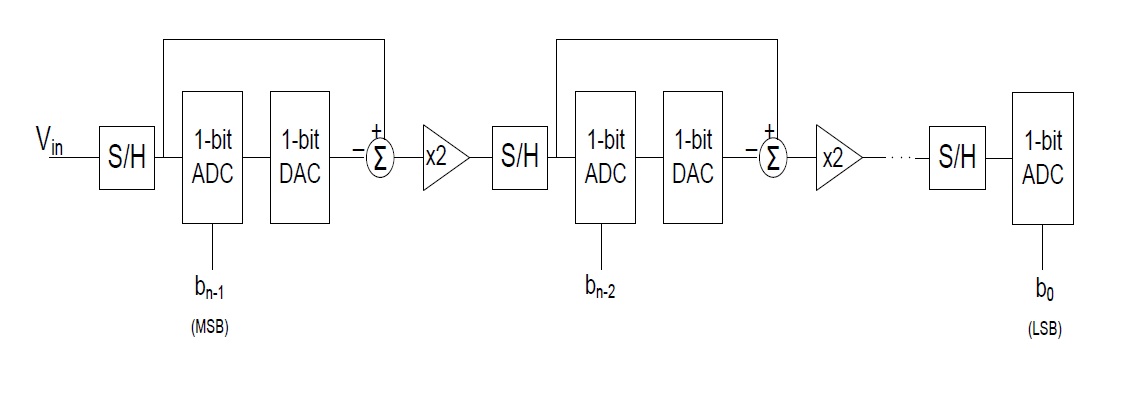

Ещё один вид архитектуры получается из развития двухступенчатого варианта АЦП - конвейерный. На каждой стадии используются одноразрядные преобразователи. В итоге получается количество бит в точности равное количеству шагов. Для организации конвейера необходимо использовать устройство выборки/хранения(S/H).

- Достоинства:

- Меньшая аппаратная сложность.

- Высокая пропускная способность.

- Недостатки:

- Необходимость калибровки.

- Необходимость использования устройства выборки/хранения.

АЦП с временным уплотнением (Time-Interleaved ADC)

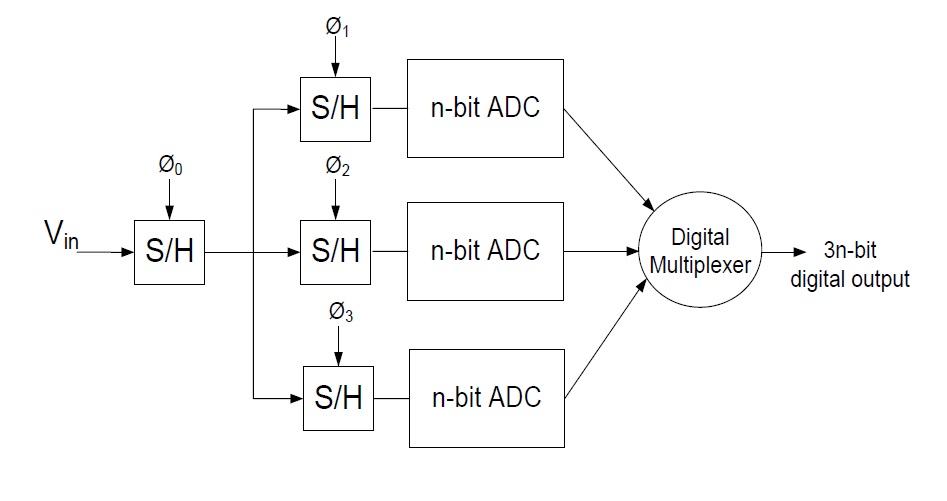

В данной архитектуре используется временное распараллеливание вычислений. На рисунке представлен пример реализации 3-канального АЦП.Тактовый сигнал O0 в 3 раза быстрее чем O1,O2,O3.Первый канал обрабатывает текущие входные данные, в то время как 2 и 3 обрабатывают данные с предыдущих циклов. В данной схеме задержка определяется только самым первым тактовым сигналом, поэтому теоретически можно увеличивать скорость работы и точность при наращивании числа каналов и сохраняя линейный рост энергопотребления и занимаемой площади на кристалле. Однако, это сложно реализовать из-за наличия шумов в тактовых сигналов.

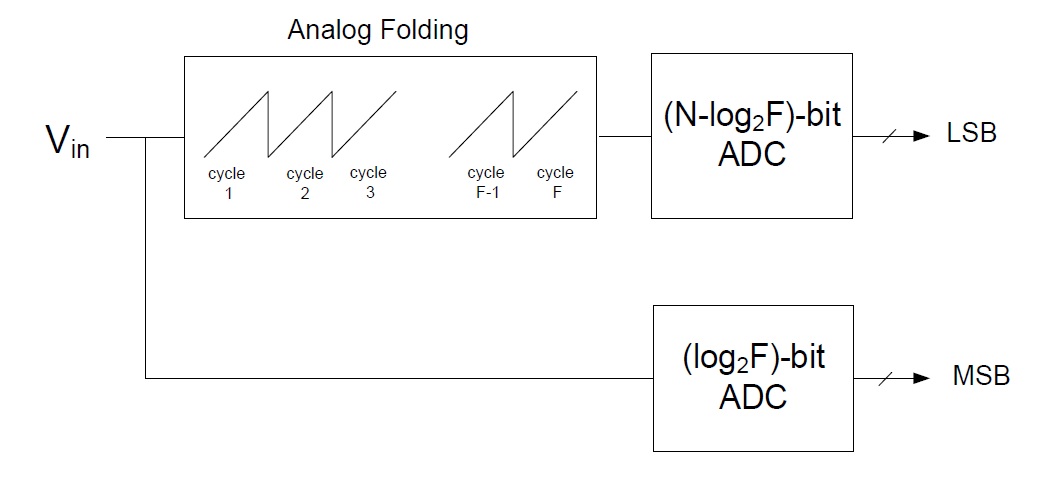

АЦП последовательного счёта (Folding ADC)

Одним из способов уменьшить количество предусилителей и сложность декодера это применение накопления.Иногда для упрощение общей архитектуры накопление используется совместно с интерполяцией.

- Достоинства:

- Достаточно высокое быстродействие.

- Отсутствие необходимости в ЦАП.

- Уменьшение энергопотребления, площади и входной ёмкости.

- Недостатки:

- Ограниченное разрешение.

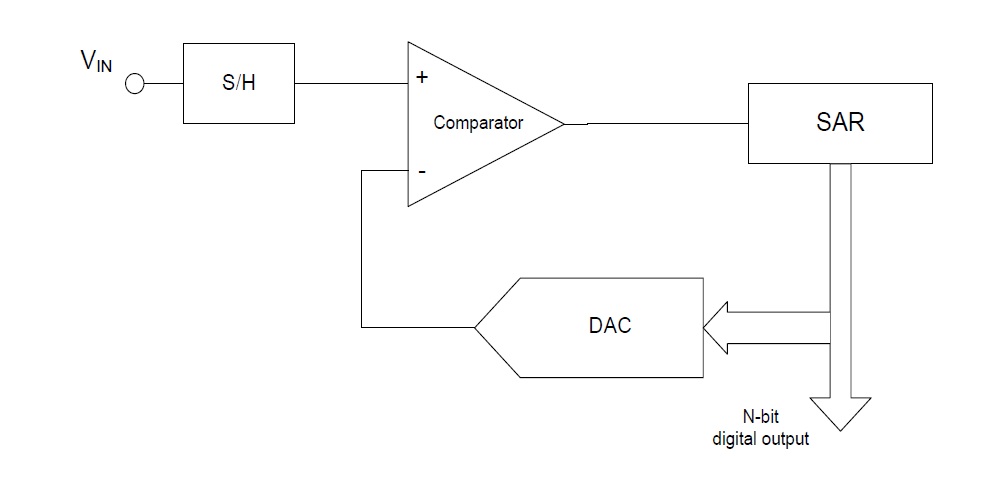

АЦП последовательного приближения (Successive Approximation ADC, SAR ADC)

АЦП последовательного приближения реализует алгоритм «взвешивания», восходящий еще к Фибоначчи. Он измеряет величину входного сигнала, осуществляя ряд последовательных «взвешиваний», то есть сравнений величины входного напряжения с рядом величин, генерируемых следующим образом:

1.На выходе ЦАП устанавливается половина опорного напряжения.

2.Если сигнал больше этой величины, то он сравнивается с напряжением, лежащим посередине оставшегося интервала, т.е., в данном случае, 3/4 опорного. Если сигнал меньше установленного уровня, то следующее сравнение будет производиться с меньшей половиной оставшегося интервала (т.е. с уровнем 1/4 опорного).

3.Шаг 2 повторяется N раз. Число шагов равно числу бит в результате.

- Достоинства:

- Высокое разрешение.

- Маленькая входная ёмкость.

- Аппаратная простота и маленькое энергопотребление.

- Недостатки:

- Маленькая скорость по сравнению с параллельным АЦП.

- Необходимость в ЦАП.