Результаты синтеза двоичных умножителей (3 - 64 бит)

Материал из Модулярная арифметики

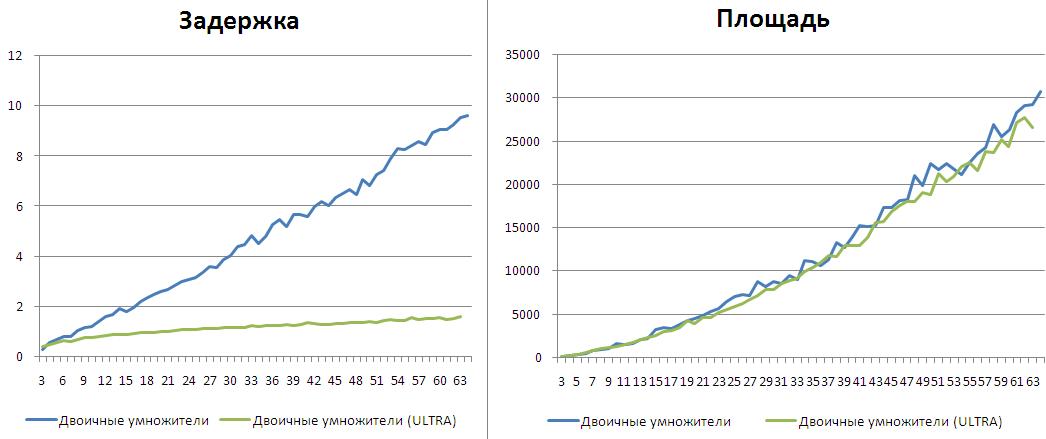

Был проведен синтез двоичных умножителей в диапазоне [3;64] бит. Синтез проводился с помощью САПР Synopsys Design Compiler. Вопрос связанный с оптимальностью используемой архитектуры бинарных умножителей САПРом остается открытым.

18.10.13 UPDATE: Был добавлены графики бинарных умножителей, синтезированные с настройкой Design Compiler ULTRA.

Содержание

Типовой Verilog-модуль

module mult_8(dataout, dataa, datab); parameter WIDTH = 8; input [WIDTH-1:0] dataa; input [WIDTH-1:0] datab; output [2*WIDTH-1:0] dataout; assign dataout = dataa * datab; endmodule

Библиотека стандартных ячеек

NangateOpenCellLibrary.lib

Скрипт для запуска

lappend search_path "../libs" "../src" set target_library "NangateOpenCellLibrary.db" set link_library [list "*" $target_library] analyze -f <имя модуля>.v elaborate <имя модуля> uniquify current_design <имя модуля> check_design set_load [load_of [get_lib_pins NangateOpenCellLibrary/INV_X4/A]] [all_outputs] set_driving_cell -lib_cell DFFRS_X2 -library NangateOpenCellLibrary -pin Q [all_inputs] set_max_delay -to [all_outputs] 0 set_max_area 0 compile report_timing > result/timing_<имя модуля>.rpt report_area > result/area_<имя модуля>.rpt remove_design -all