Генератор Verilog для умножителей на базе рекурсивной модулярной арифметики

Выбранная битность: 5 (Максимальное значение на выходе: 1024)Степень n для базиса 1: {2n-1, 2n, 2n+1}: 4 (Максимальное значение: 4080)

Степень n1 для базиса 2: {2n1-1, 2n1, 2n1+1}: 3 (Максимальное значение: 504 > (2n+1)2)

Базис 1: {24-1, 24, 24+1} или [15, 16, 17]

Базис 2: {23-1, 23, 23+1} или [7, 8, 9]

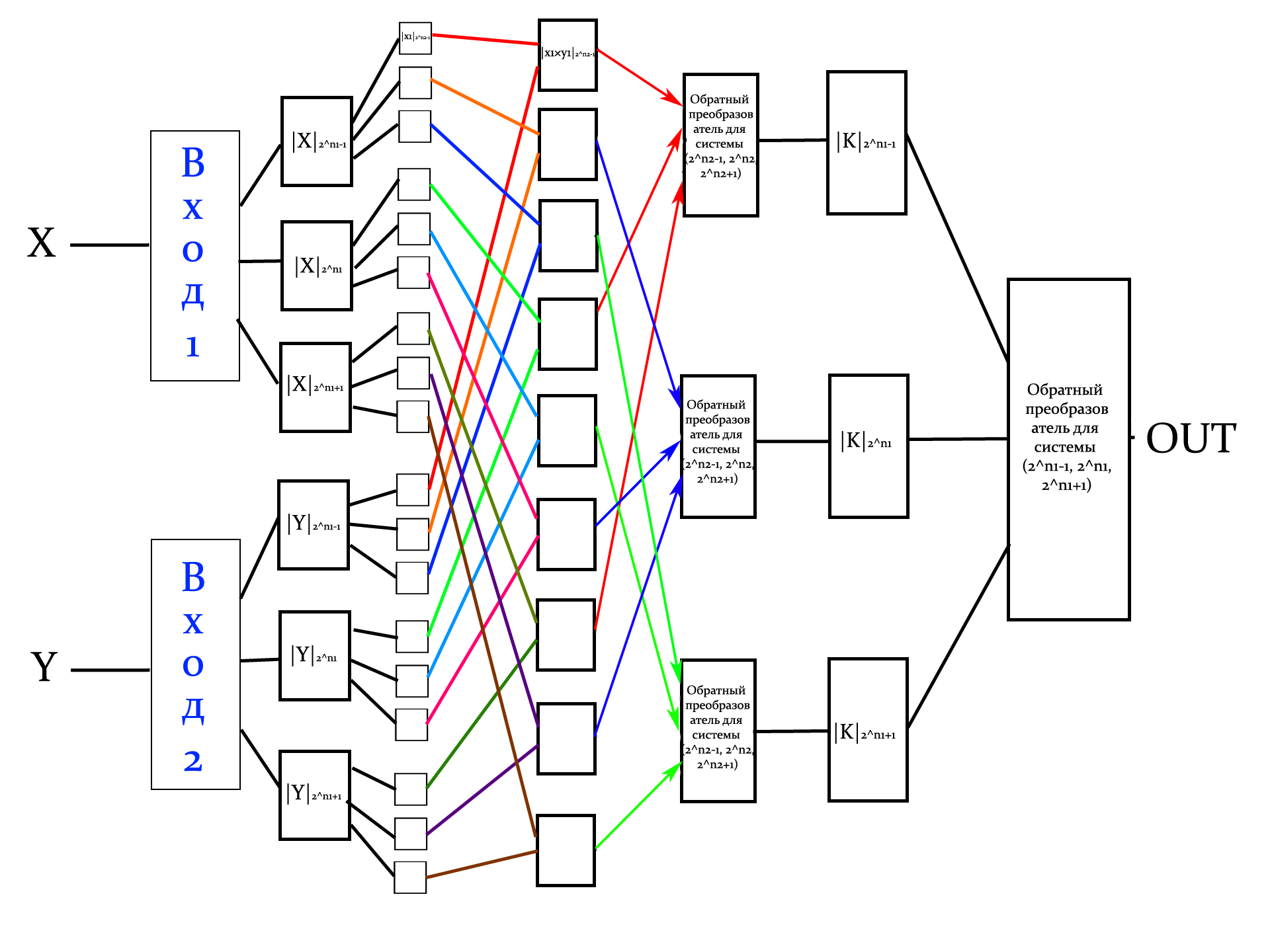

Описание: Генератор обычного двоичного умножителя вида X = A*B, где у входов разрядность n бит, а у выхода 2*n бит. Умножение выполнено на базе модулярной арифметики и специального набора модулей вида {2n-1, 2n, 2n+1}, которые применяются иерархически два раза. В итоге формируются девять параллельных каналов. Но требуется два уровня прямых и обратных преобразователей.

Схема работы

Первые результаты (05.2013): Для 32 бит метод работает медленнее и занимает больше площади, чем умножение на базе обычной модулярной арифметики в базисе {2n-1, 2n, 2n+1} Задержка: 6.87 против 4.30, площадь 43401 против 31879. Варианты ускорения: совмещение двух уровней прямых преобразователей в один за счет нового математического аппарата, совмещение обратных преобразователей и промежуточного взятия модуля между ними. Требуются исследования в этом направлении.