Результаты синтеза универсальных прямых преобразователей для простых модулей в пределах 8 бит

Материал из Модулярная арифметики

(Различия между версиями)

DimaT (обсуждение | вклад) (Новая страница: «== Описание эксперимента == Было проведено исследование универсальных прямых преобразов…») |

DimaT (обсуждение | вклад) |

||

| Строка 14: | Строка 14: | ||

== Скрипт для запуска == | == Скрипт для запуска == | ||

| − | + | *combinatorial | |

<pre> | <pre> | ||

lappend search_path "../libs" "../src" | lappend search_path "../libs" "../src" | ||

| Строка 34: | Строка 34: | ||

remove_design -all | remove_design -all | ||

</pre> | </pre> | ||

| − | + | *synchronous | |

<pre> | <pre> | ||

lappend search_path "../libs" "../src" | lappend search_path "../libs" "../src" | ||

| Строка 71: | Строка 71: | ||

== Файлы с входными данными == | == Файлы с входными данными == | ||

| − | * [http://vscripts.ru/res/files/2013_11_fwd_conv_8bit_verilog. | + | * [http://vscripts.ru/res/files/2013_11_fwd_conv_8bit_verilog.zip Verilog (zip)] |

== Файл с результатами == | == Файл с результатами == | ||

| − | * [http://vscripts.ru/res/files/2013_11_fwd_conv_8bit_result.zip Результаты | + | * [http://vscripts.ru/res/files/2013_11_fwd_conv_8bit_result.zip Результаты моделирования (zip)] |

* [http://vscripts.ru/res/files/2013_11_fwd_conv_8bit_result.xlsx Excel-таблица со сводными результатами] | * [http://vscripts.ru/res/files/2013_11_fwd_conv_8bit_result.xlsx Excel-таблица со сводными результатами] | ||

Версия 16:48, 26 ноября 2013

Содержание |

Описание эксперимента

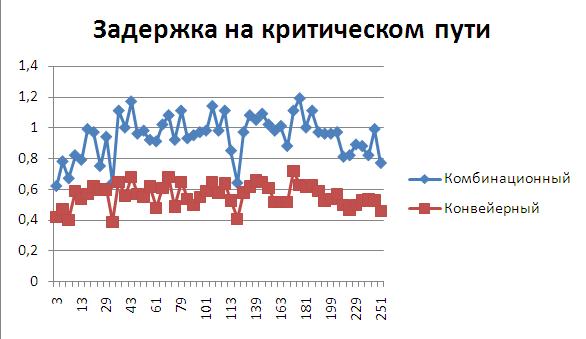

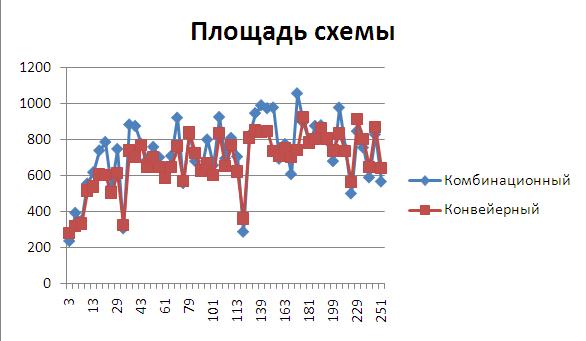

Было проведено исследование универсальных прямых преобразователей преобразователей для простых оснований в пределах 8 бит. Для тестирования использовались следующие подходы:

- Комбинационный прямой преобразователь: Пример (Модули: 3 5 7)

- Конвеерный обратный преобразователь на базе CRT II с пирамидальной структурой: Пример (Модули: 3 5 7)

Исследовались задержка на критическом пути и площадь схем.

Библиотека стандартных ячеек

NangateOpenCellLibrary.lib

Скрипт для запуска

- combinatorial

lappend search_path "../libs" "../src" set target_library "NangateOpenCellLibrary.db" set link_library [list "*" $target_library] analyze -f verilog comb_all.v elaborate forward_conv_module_x uniquify current_design forward_conv_module_x check_design -no_warnings set_load [load_of [get_lib_pins NangateOpenCellLibrary/INV_X4/A]] [all_outputs] set_driving_cell -lib_cell DFFRS_X2 -library NangateOpenCellLibrary -pin Q [all_inputs] set_max_area 0 set_max_delay -to [all_outputs] 0 compile report_timing > result2/timingx.rpt report_area > result2/areax.rpt remove_design -all

- synchronous

lappend search_path "../libs" "../src" set target_library "NangateOpenCellLibrary.db" set link_library [list "*" $target_library] analyze -f verilog seq_all.v elaborate forward_conv_module_x uniquify current_design forward_conv_module_x check_design -no_warnings set_load [load_of [get_lib_pins NangateOpenCellLibrary/INV_X4/A]] [all_outputs] set_driving_cell -lib_cell DFFRS_X2 -library NangateOpenCellLibrary -pin Q [all_inputs] set_max_area 0 create_clock clk -period 0.1 set_clock_uncertainty 0.0 [all_clocks] set_dont_touch_network [all_clocks] compile report_timing > result/timingx.rpt report_area > result/areax.rpt remove_design -all }

Результаты

Выводы

- Конвейеризация прямого преобразователя позволяет увеличить тактовую частоту почти в 2 раза, при неизменной площади.

- Общая латентность схем в тоже самое время остается практически неизменной

- Есть возможность дальнейшей конвейеризации прямого преобразователя